数字电路技术题目解答第五部分共14题

【题目7】:在计算多个TTL门电路输入端并联时的总输入电流时,为什么有时按输入端的数目加倍,有时按门的数目加倍?

【相关知识】:TTL与非门的工作原理、TTL与非门的静态特性、三极管的开关特性。

【解题方法】:通过对与非门和或非门输入级电路的分析便可一目了然。

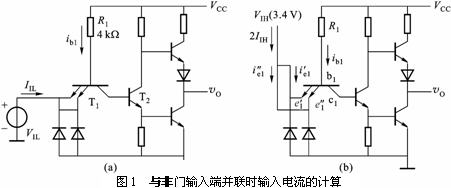

【解答过程】:在TTL电路中,与门、与非门的输入电路结构形式和或门、或非门的输入电路结构形式是不同的。由图1中可以看到,从与非门输入端看进去是一个多发射极三极管,每个发射极是一个输入端。而在图3所示的或非门电路中,从每个输入端看进去都是一个单独的三极管,而且它们相互间在电路上没有直接的联系。

1与非门输入端并联时的输入电流

由图1(a)可见,当输入为低电平时,由于处于截止状态,所以无论有几个输入端并联,总的输入电流都等于

。而且发射结的导通压降仍为0.7V。因此,总的低电平输入电流和只有一个输入端接低电平时的输入电流

相同。

当输入端接高电平时,由图1(b)可见,-b1-c1和

-b1-c1分别构成两个倒置状态的三极管,所以总的输入电流是单个输入端高电平输入电流

的两倍,也就是

乘以并联输入端的数目。

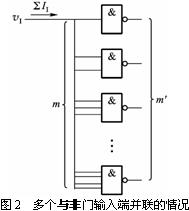

在将个与非门的m个输入端并联的情况下(如图2,显然m>

),则总的低电平输入电流为

式中是并联的与非门的个数,而不是输入端m的数目。

总的高电平输入电流为

,式中m是并联输入端的数目。

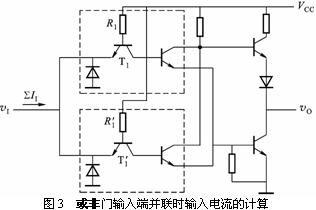

2 或非门输入端并联时的输入电流

由图3可见,从或非门的每个输入端看进去都是一个独立的三极管,因此在将n个输入端并联后,无论总的高电平输入电流Σ还是总的低电平输入电流Σ

都是单个输入端输入电流的n倍,即

,

式中的、

是单个输入端的高电平输入电流和低电平输入电流。在将多个不同或非门的n个输入端并联时,上面的两个式子仍然适用。

【题目8】:门电路的平均传输延时是如何计算的,它的大小与开关速度有什么关系?

【相关知识】:TTL与非门的工作原理、TTL与非门的动态特性、TTL与非门的开关特性。

【解题方法】:从门电路的输入、输出方波中定义平均传输时间。

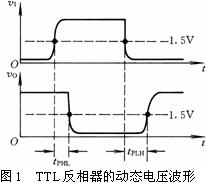

【解答过程】:在TTL电路中,由于二极管和三极管从导通变为截止或从截止变为导通都需要一定的时间,而且还有二极管、三极管以及电阻、连接线等的寄生电容存在,所以把理想的矩形电压信号加到TTL反相器的输入端时,输出电压的波形不仅要比输入信号滞后,而且波形的上升沿和下降沿也将变坏,如图1所示。我们把输出电压波形滞后于输入电压波形的时间叫做传输延迟时间。通常将输出电压由低电平跳变为高电平时的传输延迟时间记作,把输出电压由高电平跳变为低电平时的传输延迟时间记作

。

和

的定义方法如图1所示。平均传输延迟时间

定义为

(1)

TTL门电路的传输延迟时间一般为几十纳秒,延迟时间越长,说明门的开关速度越低。

因为传输延迟时间和电路的许多分布参数有关,不易准确计算,所以和

的数值最后都是通过实验方法测定的。这些参数可以从产品手册上查到。

【题目9】:为什么TTL门电路的输出级采用推拉式结构?它对减少输出电阻有什么好处?

【相关知识】:TTL与非门的工作原理、TTL门电路的主要参数、TTL与非门的开关特性。

【解题方法】:通过分析推拉式输出级在低电平和高电平输出时的工作状态,便可一目了然。

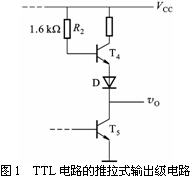

【解答过程】:在图1所示的门电路推拉式输出级中,当输出低电平时,截止,而

饱和导通。双极型三极管饱和导通状态下具有很低的输出电阻。在74系列的TTL电路中,这个电阻通常只有几欧姆,所以若外接的串联电阻在几百欧姆以上,在分析计算时可以将它忽略不计。

当输出为高电平时,截止而

导通。

工作在“射极输出”状态。已知射极输出器的最主要特点就是具有高输入电阻和低输出电阻。在模拟电子技术基础教材中,对这一特性都有详细的说明。根据理论推导,图1电路的高电平输出电阻为

上式中的(rbe4)是发射结的导通电阻,

是

的电流放大系数,

是二极管D的导通电阻。74系列TTL门电路的高电平输出电阻约在几十欧至一百欧之间。显然,这个数值比低电平输出电阻大得多。正因为如此,我们总是用输出低电平去驱动输出负载。

| 上一页1234567下一页 |