数字电路技术题目解答第五部分共14题

【题目14】:CMOS逻辑电路在使用中有哪些注意事项?

【相关知识】:CMOS反相器的结构、工作原理,复合CMOS逻辑门。

【解题方法】:分析CMOS反相器处在不同输入条件下可能出现的问题,从而提出一系列防护措施。

【解答过程】:CMOS电路使用中应当注意

一、 输入电路的静电防护

虽然在CMOS电路的输入端已经设置了保护电路,但由于保护二极管和限流电阻的几何尺寸有限,它们所能承受的静电电压和脉冲功率均有一定的限度。

CMOS集成电路在储存、运输、组装和调试过程中,难免会接触到某些带静电高压的物体。例如工作人员如果穿的是由容易产生静电的织物制成的衣裤,则这些服装摩擦时产生的静电电压有时可高达数千伏。假如把这个静电电压加到CMOS电路的输入端。将足以使电路损坏。

为防止由静电电压造成的损坏,应注意以下几点:

1 在储存和运输CMOS器件时不要使用易产生静电高压的化工材料和化纤织物包装,最好采用金属屏蔽层作包装材料。

2 组装、调试时,应使电烙铁和其他工具、仪表、工作台台面等良好接地。操作人员的服装和手套等应选用无静电的原料制作。

3 不用的输入端不应悬空。

二、 输入电路的过流保护

由于输入保护电路中的钳位二极管电流容量有限,一般为1mA,所以在可能出现较大输入电流的场合必须采取以下保护措施:

1 输入端接低内阻信号源时,应在输入端与信号源之间串进保护电阻,保证输入保护电路中的二极管导通时电流不超过1mA。

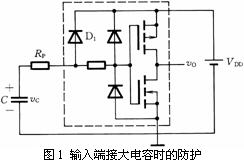

2 输入端接有大电容时,亦应在输入端与电容之间接入保护电阻,如图1所示。

在输入端接有大电容的情况下,若电源电压突然降低或关掉,则电容C上积存的电荷将通过保护二极管放电,形成较大的瞬态电流。串进电阻

以后,可以限制这个放电电流不超过1mA。

的阻值可按

=

/1mA计算。此处

表示输入端外接电容C上的电压(单位V)。

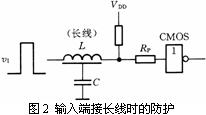

3 输入端接长线时,应在门电路的输入端接入保护电阻,如图2所示。

因为长线上不可避免地伴生有分布电容和分布电感,所以当输入信号发生突变时只要门电路的输入阻抗与长线的阻抗不相匹配,则必然会在CMOS电路的输入端产生附加的正、负振荡脉冲。因此,需串入限流。根据经验,

的阻值可按

=

/1mA计算。输入端的长线长度大于10米以后,长度每增加10米,

的阻值应增加1kΩ。

三、 CMOS电路锁定效应的防护

锁定效应(Latch-Up),或称为可控硅效应(Silicon Controlled Rectifer)是CMOS电路中的一个特有问题。发生锁定效应以后往往会造成器件的永久失效,因而了解锁定效应的产生原因及其防护方法是十分必要的。

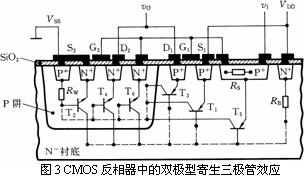

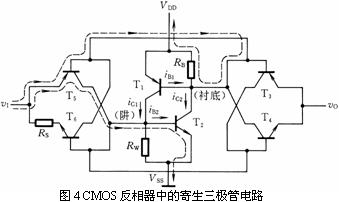

从图CMOS反相器的结构图上可以看到,为了在同一片N型衬底上同时制作P沟道和N沟道两种类型的MOS管,并利用反相PN结实现隔离,就必须先在N型衬底上形成一个P型区—P阱,然后再于P阱上制作两个N型区,形成N沟道MOS管的源极和漏极。P阱里的另一个N型区是输入保护二极管的负极。这样一来,便在三个N型区—P阱—N型衬底之间形成了三个纵向NPN型寄生三极管

、

和

。

为了得到P沟道MOS管,又在N型衬底上另外制作了两个P型区,作为P沟道管的源极和漏极。图中最右边一个P型区是输入保护电阻。这样在三个P型区—衬底—P阱之间又形成了三个横向PNP型寄生三极管、

和

。

若以表示P阱的电阻,以

表示衬底的电阻,其他高掺杂区的内阻略而不计,则这些寄生三极管和

、

一起便形成了图4所示的寄生三极管电路。其中

、

和

、

接成了一个正反馈电路,构成了可控硅结构。

如果和

的电流放大系数乘积

,那么当

有基极电流

流过时,集电极有电流

。假定

的分流作用可以忽略,则

的基极电流为

。如果再忽略

的分流作用,这时将有

,所以由于正反馈作用

被放大了。于是

、

的电流都迅速增长,直至不能再增大为止。而且,除非切断电源或将电源电压降至很低,这种导通状态将一直保持下去,因此把这种现象叫做锁定效应。

同理,有基极电流注入时也会引发锁定效应。

那么什么条件下或

会导通呢?从图4上可以看出:

1 若>

+

(

表示

~

发射结的正向导通压降),则

导通,并进而引起

导通,产生锁定效应。图中用虚线示出了

基极电流和集电极电流的流向。

的集电极电流流入

的基极,形成可控硅的触发电流。

2 若<-

,则

导通,并进而引起

导通,产生锁定效应。

3 若>

+

,则

导通,并进而引起

导通,产生锁定效应。

4 若<-

,则

导通,并进而引起

导通,产生锁定效应。

5 若大于PN结的反向击穿电压,则

或

也会导通,并引发锁定效应。

因此,为防止发生锁定效应,在CMOS电路工作时始终应保证、

、

的数值符合如下规定:

-<

<

+

,-

<

<

+

<

(

端的击穿电压)

此外,还可以采取以下的防护措施:

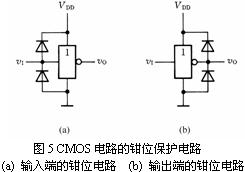

(1)在输入端和输出端设置钳位电路,以确保和

不会超过上述的规定范围,如图5所示。图中的二极管通常选用导通压降较低的锗二极管或肖特基势垒二极管。

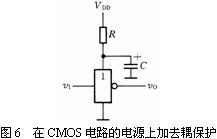

(2)在可能出现瞬时高压时,在CMOS电路的电源输入端加去耦电路,如图6所示。在去耦电阻R选得足够大的情况下,还可以将电源电流限制在锁定状态的维持电流以下,即使有触发电流流入

或

,自锁状态也不能维持下去,从而避免了锁定效应的发生。这种方法的缺点是降低了电源的利用率。

(3)当系统由几个电源分别供电时,各电源的开、关顺序必须合理。启动时应先接通CMOS电路的供电电源,然后再接通输入信号和负载电路的电源。关机时应先关掉信号源和负载的电源,再切断CMOS电路的电源。

为了使用的安全和方便,人们一直在研究从CMOS电路本身的设计和制造上克服锁定效应的方法。现在一些工厂生产的高速CMOS电路中,通过改进图版设计和生产工艺,减小了寄生三极管的β值和、

的阻值,已经能够基本消除锁定效应的发生。但这些改进方法都明显地加大了芯片面积,因而目前还不能保证所有的CMOS电路产品都不会发生锁定效应。

| 上一页1234567 |