数字电路技术题目解答第三部分共10题

【题目3】:如何用译码器实现多输入变量、多输出函数的设计?

【相关知识】:译码器的输出和输入逻辑关系、逻辑函数的最小项表达式等。

【解题方法】:将一逻辑函数的变量有序地加到译码器的输入端,则译码器每一个输出函数将对应于输入代码的一个最小项,再通过门电路实现逻辑函数。

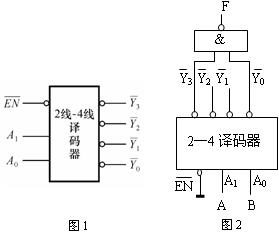

【解答过程】:译码器的每一个输出函数对应输入代码的一个最小项。如2线—4线译码器(见图1),当使能控制端时,

,

,

,

,译码器的这一特性可用来实现逻辑函数。

如果将一逻辑函数的变量有序地加到译码器的输入端,则译码器每一个输出函数将对应于输入变量的一个最小项,因此,译码器可用以实现组合逻辑电路的设计。如用2—4译码器实现函数,只要将A、B分别接到地址

、

,则:

,如图2所示连接。

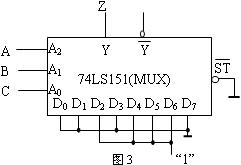

【题目4】:如何用数据选择器作逻辑函数发生器实现任意组合逻辑电路的设计?

【相关知识】:数据选择器的输出和输入逻辑关系、逻辑函数的最小项表达式等。

【解题方法】:先将逻辑函数用卡诺图或最小项之和形式表示出来,再和数据选择器的输出函数比较,将变量以一定的形式接到数据选择器的输入端,输出为要求实现的逻辑函数。

【解答过程】:数据选择器的输出函数和逻辑函数的最小项之和式(即与或表达式)一致,因此可用来实现任意组合逻辑函数。

采用数据选择器设计逻辑电路时,可按以下步骤进行:

1、把函数的输入变量分为两组,一组加到数据选择器的地址端,余下的一组变量送到数据选择器的数据输入端。

2、求出加到每个数据输入端的值。

3、画出要实现的逻辑函数的逻辑图。

具体设计方法分三种情况说明:

①采用具有n个地址端的数据选择器实现n变量的函数时,应将函数的输入变量加到地址端(A),将函数卡诺图各方格内的值接到相应的数据输入端(D)。

②当函数输入变量数小于数据选择器的地址端时,应将不用的地址端及不用的数据输入端都接0(或接1)。

③当函数输入变量大于数据选择器地址端时,可任选几个变量接到地址端,剩下的变量以一定的方式接到数据端。

下面举例说明。

例.试用一片74LS151型8选1数据选择器实现逻辑函数:

解:用数据选择器实现逻辑函数时要先将逻辑函数用卡诺图或最小项之和形式表示出来,再和数据选择器的功能比较。

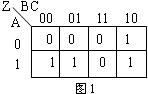

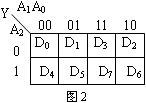

(1)函数的卡诺图为图1:

将A、B、C接到地址端、

、

,Y作为输出Z,则和8选1数据选择器卡诺图(图2)相比较:

得:

如图3连接:

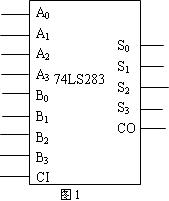

【题目5】:如何用加法器实现组合逻辑功能?

【相关知识】:加法器的功能、逻辑函数的真值表等。

【解题方法】:将逻辑函数转化成输入变量与输入变量或输入变量与常量在数值上相加的形式,再用加法器来设计这个组合逻辑电路。

【解答过程】:如果要产生的逻辑函数能化成输入变量与输入变量或输入变量与常量在数值上相加的形式,这时用加法器来设计这个组合逻辑电路往往会非常简单。如加法器经常用来作码制之间的转换。

举例说明。

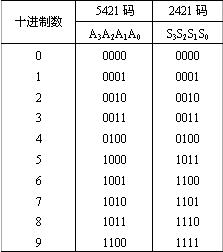

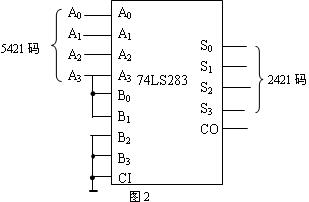

例.用四位二进制加法器74LS283将5421BCD码转换为2421BCD码。74LS283的简化逻辑图如图1所示,和

是两个加数,CI是低位来的进位输入,

是产生的和,CO是进位输出。

解:加法器可用作两种码制之间的转换。

首先列出两种编码的对照表:

分析二种编码可以发现,对十进制数0~4,两种编码完全相同,若将5421BCD码接到被加数端,则加上0000,得到和即为 2421BCD码;对十进制数5~9,2421码比5421码多0011,若将5421BCD码接到被加数端,则加上0011,得到和即为2421BCD 码。再分析5421码可以发现,当输入为0000~0100时,最高位为0,当输入从1000~1100时,最高位为1,因此可利用输入的5421码的最高位来控制加法器的加数是0000或是0011,以获得输出为2421码。如图2所示。

| 上一页1234下一页 |