数字电路技术题目解答第四部分共11题

【题目1】:如何理解数码寄存器和锁存器在时序电路中的作用?

【相关知识】:数码寄存器结构,时序电路信号分类,集成电路输出方式等。

【解题方法】:数码是最简单的时序电路,其主要作用是并行寄存数据。掌握寄存器的输入控制方式,了解寄存器的输出方式是应用数字寄存器的关键。

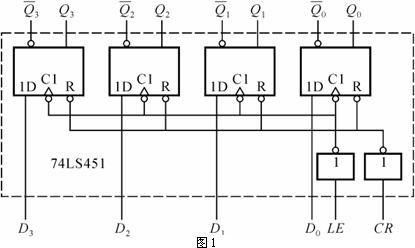

【解答过程】:图1是74LS451中规模集成并行数码寄存器。数码寄存器的输入信号可分成三种:

(1) 锁存使能控制端,如图1中的LE。只有当锁存使能信号有效(图1是上升沿)时,寄存器才能锁存输入数据(d3d2d1d0),寄存器状态得到更新。时钟信号经常作为锁存使能端的输入,以便协调时序电路的工作。

(2) 控制输入端,它的作用可同时影响寄存器的多个输出,如图1中的CR。有些控制输入端需要与锁存使能输入端配合才能生效,称这种控制为同步控制。例1的清零属于异步控制。

(3) 数据输入端,如图1的。

在微控制器单元(MCU)中,寄存器是十分重要的资源。寄存器的主要作用是快速寄存算术逻辑运算单元(ALU)运算过程中的数据。熟悉和了解MCU的寄存器是掌握MCU应用的关键。MCU内部寄存器的位数通常与MCU的总线宽度相同,如普通51系列单片机的寄存器宽度是8位,嵌入式控制器和DSP处理器的寄存器宽度通常是32位或48位。

当寄存器应用在MCU单元的外部时,由独立的一片中规模集成电路组成,通常称之为锁存器。常用的8位锁存器有74LS373,74LS374,74LS377,74LS573等。

应用锁存器时了解锁存器的锁存使能输入端的有效方式,控制输入端的控制方式和输出端的输出形式十分重要。

锁存使能输入控制方式有:低电平有效,高电平有效,时钟上升沿有效,时钟下降沿有效。

控制输入端有:异步清零,异步置数,同步清零,同步置数。

输出形式:普通TTL输出,OC输出,三态输出。

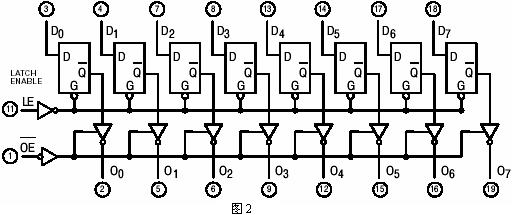

例1,74LS373的结构如图2所示,试分析其输入控制方式和输出方式。

观察74LS373逻辑电路图,配合74LS373提供的数据手册可知74LS373是高电平触发、低电平输出全能控制、输出具有三态功能的8位锁存器。

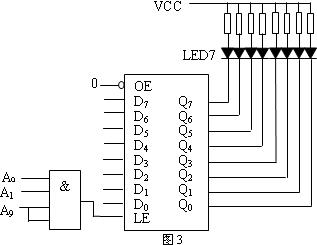

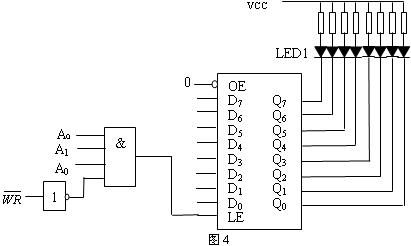

图3是应用74LS373中写入数据、控制8个LED指示灯状态的一个电路图。

需要改变指示灯状态的时序过程:

(1) 准备输入数据(例,需要灯LED0、LED2、LED4、LED6亮时,令

);

(2) LE控制输入置高电平,即令,将输入锁入寄存器;

(3) LE控制输入置低电平,使锁存器处在保持状态。

正常情况只要锁存使能输入无效,即使输入数据变化,输出指示灯的状态也不会变化。但是,当

受到干扰时,出现

时,正在变化的输入会被锁存入寄存器,使输指示灯的状态混乱。图3电路的抗干扰能力不强。

图4在锁存器的锁存使能控制端增加了一个条件,当写信号 和地址信号同时有效时,锁存器才能锁存输入数据。这样即使

信号(地址)受干扰,只要此时没有写信号,锁存器状态就不会改变,从而增加电路的抗干扰能力。

【题目2】:如何理解同步清零(置数)和异步清零(置数)的区别?

【相关知识】:中规模集成计数器的功能表阅读、反馈清零法和反馈置数法的应用等。

【解题方法】:中规模集成计数器的模通常是10或16,当要实现比集成计数器模小的计数器时,必须使用清零或置数端,应用的关键区分清零和置数是同步还是异步。

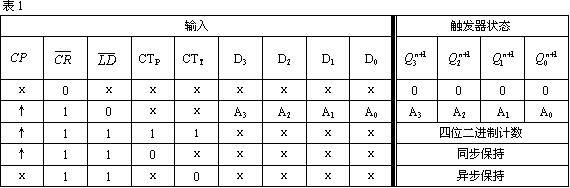

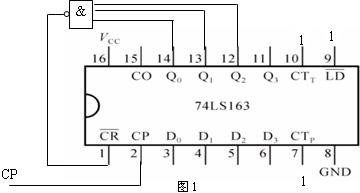

【解答过程】:[例1]表1是单片集成计数器74LS161的功能表,图1是由单片集成计数器74LS161构成的计数器,试分析其逻辑功能。

[解]由图1可知,集成计数器控制端(有效),置数端

(无效),该设计应用了集成计数器功能表中的四位二进制计数功能。但清零端

,而是受状态(q2)、(q1)和(q0)的控制,目的应用反馈清零法改变计数顺序。

当时,清零控制端有效,此时能否立即实现清零将由清零控制的同步或异步特性决定。

异步控制不需要时钟有效沿的配合,只要控制端满足条件就能实现控制功能。同步控制当控制端满足条件后,还需要等待时钟有效沿,且时序不能颠倒,只能这样才能实现控制功能。

由表1可知,74LS161的清零控制与时钟无关,属于异步控制。当时,清零控制端有效,立即实现清零功能,

,

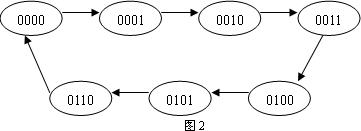

仅是一个短暂的过渡状态。图1的状态转移图如图2所示。

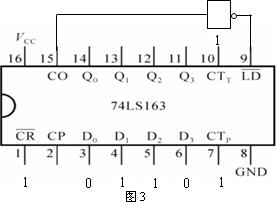

[例2]图3是由单片集成计数器74LS161构成的时序电路,试分析其逻辑功能。

[解] 由图3可知,集成计数器控制端(有效),清零端

(无效),该设计应用了集成计数器功能表中的四位二进制计数功能。但置数端

,而是受状态(q3)、(q2)、(q1)和 (q0)(

)的控制,目的应用反馈置数法改变计数顺序。

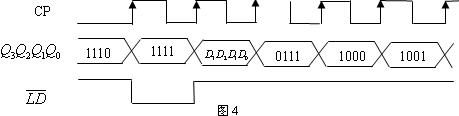

由表1可知,74LS161的置数控制需要时钟有效边沿配合,属于同步控制。当时,置数控制端有效,但必须等待时钟边沿到达后才能实现置数功能,故状态

不会立即被置数输入端

替换,而会保持一个时钟脉冲的宽度,且在此间

,一直有效,当下一个时钟有效沿到来时实现同步置数,

。同步置数过程如图4所示。

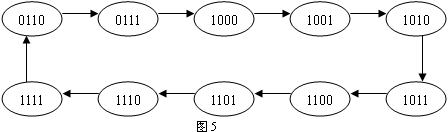

由此可得完整状态转换图如图5。

| 12345678下一页 |