数字电路技术题目解答第三部分共10题

【题目6】:如何用加法器实现减法运算?

【相关知识】:加法器的功能、利用补码将减法转化成加法等。

【解题方法】:在二进制减法运算中,一般采用将减数求补,再与被减数相加的方法求差。

【解答过程】:设A=和B=

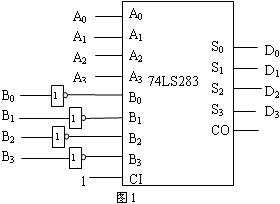

是四位二进制正整数,且A>B。试用四位二进制加法器74LS283及最少的门实现减法计算D=A-B 在二进制减法运算中,一般采用将减数求补,再与被减数相加的方法求差。四位二进制数

的补码为

,由此将减法转化为加法。得到四位减法电路如图1所示。

【题目7】:如何识别竞争冒险现象,怎样消除冒险现象?

【相关知识】:门的传输延迟时间、竞争、冒险、卡诺图、冗余项等。

【解题方法】:先用代数法或卡诺图法识别竞争冒险现象,再讨论消除冒险现象的方法。

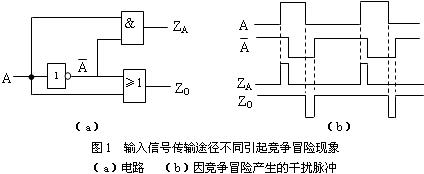

【解答过程】:由于门电路普遍存在传输延迟时间,输入信号经过不同途径传输后,到达同一个门的输入端的时间有早有迟,这种时间差别的现象称为竞争。有的竞争不会产生错误输出,称非临界竞争,有的竞争要产生错误输出,称临界竞争,或称冒险。

在图1(a)电路中,在不考虑传输时间时,与门输出,或门输出

。若考虑延迟时间,则在输入信号A的作用下,将得到如图1(b)所示波形。由波形图可见,ZA波形中出现正尖脉冲,使ZA不能恒为0,ZO输出波形中出现负尖脉冲,使ZO不能恒为1,引起竞争冒险现象。

一、 可以用代数法和卡诺图法来判断一个电路是否存在冒险现象。

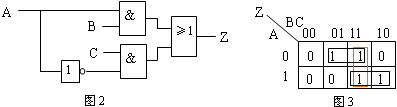

如图2电路,当B=C=1时

,存在以上

型冒险。

也可用卡诺图法来判断。画出卡诺图如图3所示,和

的包围圈是与项

,

和

的包围圈是与项

。在B=C=1时,包围圈(1,3)代表

,包围圈(6,7)代表A,因此

存在冒险。当两个圈之间彼此包含有相邻项(这里是

和

),且此两个包围圈之间没有公共部分,则这两个包围圈的和式存在冒险。

二、要消除冒险现象,可采取几种方法:

1、在与—或表达式中增加冗余项

的冗余项是BC,加上冗余项后,使逻辑表达式变成

,此时当B=C=1,使Z=1,于是,消除了在B=C=1时的冒险现象。

2、设禁止脉冲

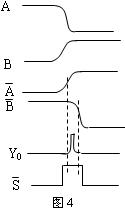

在输入信号可能发生竞争冒险的时间内,用一个禁止脉冲将有关门封锁。以译码器中的输出为例。

输入信号AB接到译码器地址,当输入信号AB由10变为01时,由于传输时间不一样,使

、

的波形如图4所示,输出

产生一个正干扰脉冲。利用译码器的使能端

可消除竞争冒险现象,只要在引起竞争冒险的传输时间内,在使能端上加1,使译码器禁止工作即可,见图4所示。

此外,在输出端接一个几百PF的滤波电容,将输出的干扰脉冲滤去,但此电容也会使电路的输出波形的边沿变坏,因此,一般只用于工作速度不高的电路中。

组合逻辑电路和异步时序逻辑电路中都存在冒险现象,但是在时序电路中包含有大量组合电路,故对组合逻辑电路的冒险现象要更加注意。

【题目8】:如何从触发器的图形符号认识其功能和触发方式?

【相关知识】:高电平触发、低电平触发、上升沿触发、下降沿触发、直接置0端、直接置1端等。

【解题方法】:由触发器逻辑符号了解触发器的时钟触发方式及其它功能。

【解答过程】:采用触发器逻辑符号,可以在没有看到触发器复杂的内部电路的情况下,仍能了解触发器外部的输入和输出之间的逻辑关系。

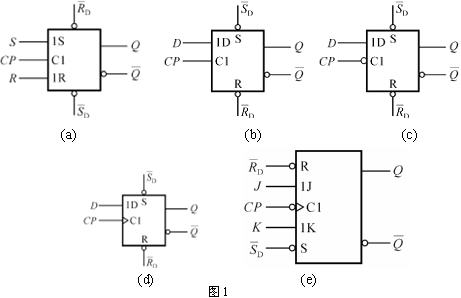

图1符号中都有C1,是控制关联作用端,即C1是产生操作的输入端(即触发器的时钟脉冲CP输入端)。C1中的C是控制关联标记,受C1关联作用的输入是以数字1标记的,例如,1S、1R、1D、1J、1K等,都受C1控制。JK触发器中的1J和1K表示受同一个C1关联作用的J输入和K输入,若有第二个时钟C2,受其控制的输入用2J和2K表示。

图1(a)和(b)表示高电平触发的钟控RS触发器和D触发器,在C1为高电平时,受其关联作用的输入1S、1R和1D分别按触发器的功能对输出产生作用,输出和

会跟着产生相应的变化,而在C1为低电平时,受其关联作用的输入1S、1R和1D不会对输出产生作用,输出

和

保持原状态不变。图1(c)是低电平触发的D触发器,CP输入端引线和方框交接处画一个小圆圈,用来表示CP和C1的极性相反,表示时钟低电平有效,在时钟CP为低电平时,输出

和

会跟着输入产生相应的变化,而在时钟CP为高电平时,输出

和

保持原状态不变。

图1(d)和(e)表示边沿触发的D触发器和JK触发器,这类逻辑符号中有动态符号“>”,(d)表示上升沿触发的D触发器,C1处在上升沿时,输出随D的作用而变化;(e)表示下降沿触发的JK触发器,CP输入端引线和方框交接处画一个小圆圈,触发器在CP下降沿时受输入作用改变输出的状态。直接置0端和直接置1端

表示低电平有效,它们的输入端引线和方框交接处都画一个小圆圈,当

和

分别为0时,将触发器分别直接置0和直接置1。

| 上一页1234下一页 |