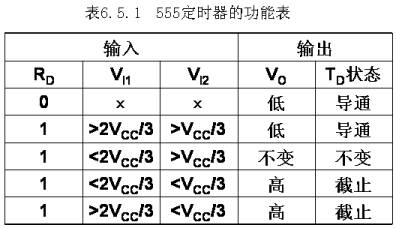

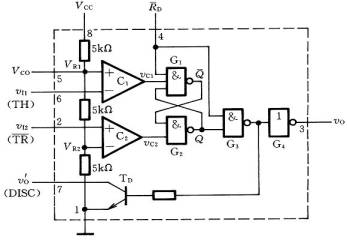

555时基集成电路内部电路图

发布时间 2008-05-23

555时基集成电路是美国Signetics公司于1972年研制的用于取代机械式定时器的中规模集成电路,因输入端设计有三个5kΩ的电阻而得名。555定时器是一种多用途的模拟电路与数字电路混合的集成电路,可以方便的构成施密特触发器,单稳态触发器和多谐振荡器。目前,流行的产品主要有4个:BJT两个:555,556(含有两个555);CMOS两个:7555,7556(含有两个7555)。

555定时器可以说是模拟电路与数字电路结合的典范。

555时基集成电路内部电路图

555定时器有两个比较器 C1和 C2各有一个输入端连接到三个电阻R组成的分压器上,比较器的输出接到RS触发器上。此外还有输出级和放电管,输出级的驱动电流可达200mA。

比较器C1和C2的参考电压分别为UR1和UR2,根据C1和C2的另一个输入端——触发输入和阈值输入,可判断出RS触发器的输出状态。当复位端为低电平时,RS触发器被强制复位。若无需复位操作,复位端应接高电平.由于三个电阻等值,所以当没有控制电压输入时

当控制电压外接时,如外接![]() ,则

,则

![]()

![]()

为防止干扰,控制电压端悬空时,应接一滤波电容到地。