电脑并行口及增强型并行口

1、电脑并行接口图及引脚定义

出现于1995年的IEEE 1284标准 2 中规定了电脑并行口的多种工作模式,包括标准并行口(SPP),增强型并行口(EPP),扩展型并行口(ECP)。其中,SPP模式的正向(电脑到外设)数据速率可以达到150kbps。但反向(外设到电脑)传输却很不方便,多次I/O才能完成一个完整数据的传输,大大降低了数据速率。

ECP与 EPP模式是依靠符合IEEE STD 1284标准的I/O控制器实现的。ECP模式虽然支持DMA操作,可以明显减轻电脑CPU的负担,但获得高性能的代价是必须设计很复杂的接口。而 EPP模式则可以通过一条OUT或IN指令将一个字节的数据传输到外设或电脑,由I/O控制器操纵所有的握手线,不需要CPU干预。由此可见,EPP模式是一种简单、高效、高速的方法。要使用EPP模式,就必须根据系统的实际情况,设计合理的接口电路,尤其要注意握手信号的设计,以保证数据交换的顺畅。

2、电脑增强型并行口

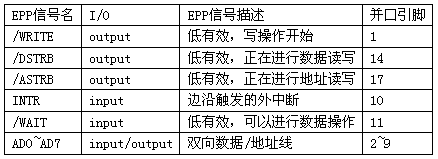

电脑并行口处于EPP工作模式时各信号线的定义如表1所示。

表1:EPP模式信号线定义

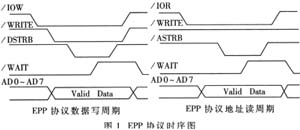

其中,最主要的两根握手线是/DSTRB和/WAIT,电脑中相应的I/O控制芯片会根据/DSTRB和/WAIT的电平转换情况自动执行或终止对并行口数据的读写操作,时序关系如图1所示。

图中未给出的EPP协议数据读周期与EPP协议地址写周期可以由此图推出。

利用INTR、/DSTRB、/WAIT握手线实现与电脑间的通信流控。从时序图可以看出,当/DSTRB与/WAIT均为低时可以对数据进行读写,而 /WAIT变为高时则认为一个I/O周期结束。所以,在外设认为一次数据传输结束时,即可将/WAIT置为高;相应地,电脑内的I/O控制芯片会置 /DSTRB为高。外设可通过INTR使电脑进入中断处理程序,开始数据的发送或接收。

因为在EPP模式下,由I/O控制器对所有的握手线进行处理,不需要CPU干预,所以电脑上的通信程序较简单。EPP协议的用户编程接口是协议定义的几个I/O地址。当并口基地址为378H时,EPP的地址寄存器为37BH,数据寄存器为37CH,对这两个寄存器的读写就可产生地址和数据的读写周期。

通过试验发现,在主频为400MHz的奔腾电脑上,没有/WAIT信号的情况下,一个EPP I/O周期最长为 2us;而在接口电路设计合适的情况下,/WAIT信号在输入数据100ns后升高,即数据稳定时间为100ns,可以保证数据传输的稳定可靠。即使再缩小数据稳定时间,数据传输仍能正常进行。从试验结果看,数据速率可达2Mbyte/s。

通常情况下,电脑并口为标准并口(SPP)模式,可以在BIOS中设置为增强型并口,也可以向I/O控制器中的控制寄存器(ECR)写入控制字来完成 EPP模式的设置。ECR的I/O端口地址为77AH。首先,向ECR端口发IN指令,存储读回的数据;然后,向ECR端口发OUT指令,写入相应的状态字,所有传输完成后,把原存储的状态字写回。