“双核”示波器的硬件描述与程序设计

2.高速AD转换与FIFO存储电路

数字示波器中最重要的电路是AD转换电路,它的作用是将被测信号采样并转换成数字信号存入存储器,说它是数字示波器的咽喉一点也不为过,因为它直接决定着数字示波器所能测量的最高频率。根据乃奎斯特定理,采样频率至少是被测信号最高频率的2倍才能复现出被测信号。

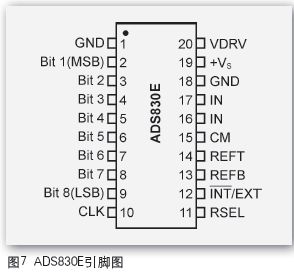

而在数字示波器中采样频率至少应该是被测信号频率的5~8倍才行,否则根本观察不到信号的波形。在本电路中我选用的AD 转换芯片为BB公司的8位高速AD转换器ADS830E,官方资料给出的采样频率为10kS/s~60MS/s,通过实验发现转换速率在1kHz以下工作也很正常,所以本示波器的最低采样频率为600S/s,要说明的一点是高速AD转换器一般都有高低端转换速率的限制,比如TLC5540,8位AD转换器,转换速率为5~40MS/s,我试过当转换频率降到2MHz以下时就不能正常工作,所以选择AD转换芯片时不仅要注意最高转换速率,还要关注最低转换速率,否则可能导致电路无法正常工作。有朋友也许会问8位转换精度会不会有点太低?其实8位转换器对于示波器来说是够用的,就拿这个电路来说,我选用的 LCD显示模块的分辨率为320×240,垂直分辨率为240格,而8位转换精度的分辨率为256格,比显示器的分辨率还高,所以绝对够用。还有就是价格及电路的设计,在最高采样率相同的情况下10位AD转换芯片的价格是8位AD转换芯片的几倍,而且位数的增加也使电路的复杂程度大大增加,将直接影响处理速度,导致屏幕刷新过慢,反而影响性能。所以本着够用的原则本示波器选用60MHz的8位AD转换芯片ADS830E。引脚排列见图7。

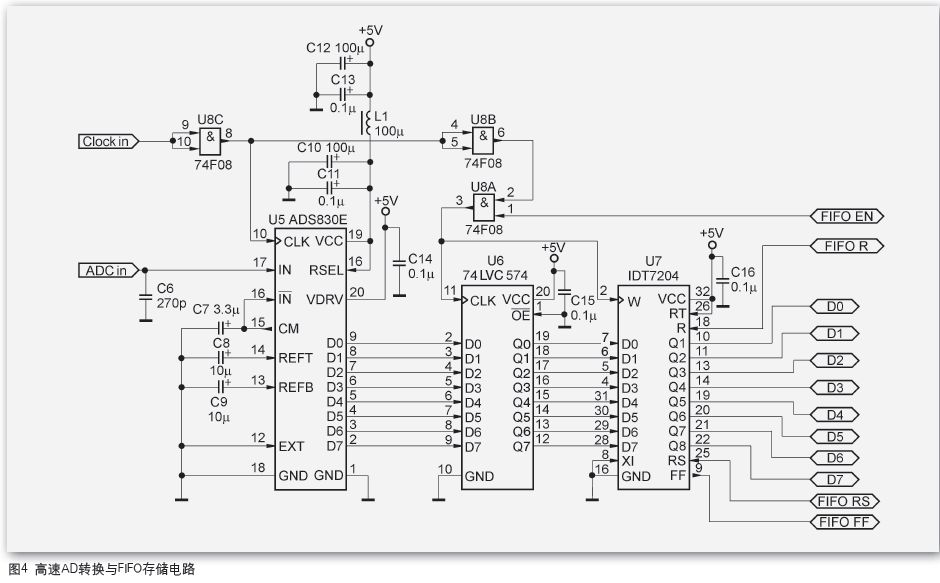

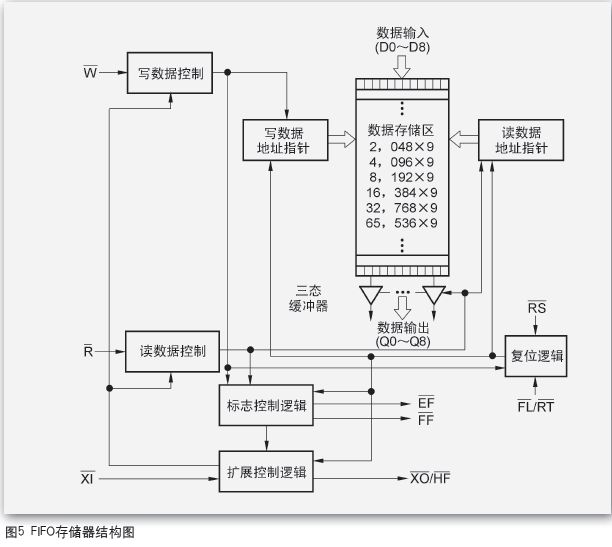

AD转换与FIFO存储电路见原理图4,由程控放大电路调整后的信号分成两路,一路进入AD转换电路进行采样, 采样所得的数据由74LVC574锁存缓冲后送入FIFO存储器。FIFO存储器是一种双口的SRAM,这种存储器没有地址线,随着写入或读取信号对数据地址指针进行递加或递减,来实现寻址。在AD转换器与MCU2之间加入FIFO的作用是起到高速数据缓冲的作用,因为AD转换器的最高工作频率为 60MHz,远高于MCU2的工作频率,所以让FIFO与AD转换器同步工作存储AD转换器的转换输出数据。FIFO存储器有3个标志位引脚,分别为 FF(满标志):当存储器存满后置位该标志,此时存储器忽略一切写数据操作。HF(半满标志):当存储器存满一半后置位该标志。EF(空标志):当存储器被读空时置位该标志,此时存储器忽略一切读数据操作。FIFO存储器结构图见图5。本电路中只用了该芯片的FF标志与MCU2的PB3相接,当FIFO存储器存满后FF引脚被拉高,通知MCU2进行数据读取,这时MCU2禁止AD转换器与FIFO存储器的时钟,FIFO的控制权交给MCU2(其实MCU2 只是禁止了FIFO存储器的写时钟,见图6,时钟信号通过U8C组成的缓冲器后直接加给了ADS830E,所以MCU2不能禁止AD转换时钟,只能通过由与门U8A组成的时钟控制开关禁止或使能FIFO存储器的时钟信号。因为实验中发现AD转换在启动后的几个时钟周期内的采样不可靠,所以就让AD转换器一直工作,通过控制FIFO存储器来控制AD采样。在AD转换电路与FIFO存储器中加入74LVC574的目的是锁存数据提高数据通道的稳定性)。

当MCU2读完数据并完成软件触发后使能AD转换器与FIFO存储器时钟,继续读取新的数据,同时MCU2对读取的数据进行处理、显示。

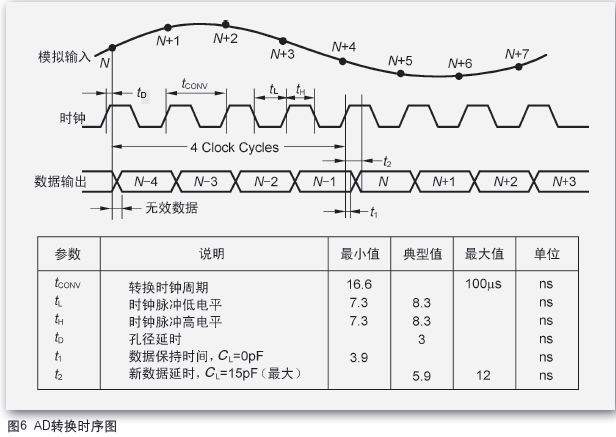

这儿再将高速数模转换器ADS830E的工作简单介绍一下,ADS830E的时序如图6所示,由图可知每个时钟周期进行一次数模转换,所以采样速率就是时钟频率,故可以很方便的通过控制采样时钟来控制采样频率,当前输出的采样数据是4个时钟周期以前采样电压的值,也就是说从采样到输出有4个时钟周期的延迟,这对我们所要做的电路并不重要,所以我们可以简单的理解为输入一个时钟脉冲转换一次,时钟脉冲的下降沿输出数据就行,应用非常方便。还有一点就是ADS830E的输入电压幅度是可以编程控制的,11脚(RSEL)为控制引脚,当11脚置高电平时,ADS830E的输入电压范围是1.5~3.5V,即2Vpp。当11脚置低电平时,输入电压范围是2~3V,即1Vpp。进行程控放大器设计时要考虑这个问题,本电路选用 2Vpp的输入电压范围。

| 上一页123456下一页 |