数字电路技术题目解答第四部分共11题

【题目3】:如何实现集成计数器的级联?

【相关知识】:中规模集成计数器的功能表阅读,反馈清零(置数)应用,计数器级联等。

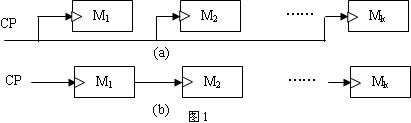

【解题方法】:当被设计计数器的容量大于单片中规模集成计数器的模时,必须通过多片级联方式实现。片间级联方式有同步级联和异步级联两种。图 1(a)各级计数器的时钟脉冲相同,称这种级联方式为同步级联。同步级联要求中规模集成计数器具有同步保持功能。图1(b)各级计数器的时钟脉冲不同,当前级时钟由前级计数器状态决定,称这种级联方式为异步级联。

设第i级由单片集成计数器构成的计数器模为(mi),则多片级联后的计数器容量等于。

大容量计数器的设计可以分成两步:第一步是应用反馈清零或反馈置数法设计第级模为(mi)的计数器(最高级的设计略有不同),第二步是完成片间级联信号的设计。

【解答过程】:

[例]应用中规模集成计数器74LS163设计一个8421BCD编码的60进制计数器。 [解] 按设计要求,60进制计数器应该分解成二级实现,且。本例采用反馈置数法实现个位10进制计数器,十位的6进制计数器采用反馈清零法实现。

十位和个位各用一片集成计数器实现,但十位的计数状态必须受个位的控制。只有当个位计数溢出时,十位才计一次数。由于74LS163具有同步保持功能,因此片间级联可以采用同步级联方式,当然也可以采用异步级联方式。

1.片间同步级联法

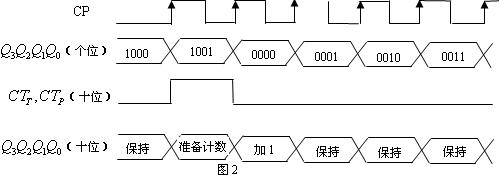

通过个位状态(q3q2q1q0)控制十位的同步保持控制端,并令

。这样,当个位计数至9,十位

,计数功能有效,当下一个时钟有效沿到来后就可实现一次计数。产生十位同步控制端的过程如图2。

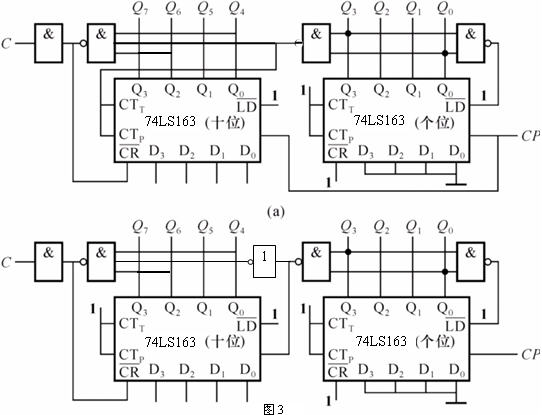

高位(十位)采用反馈清零法实现。若只考虑设计一个6进制8421BCD编码的6进制计数器,当状态等于5时就需准备好同步清零脉冲。但当设计8421BCD编码的60进制计数器时,最大输出是59,必须当十位等于5、同时个位等于9时,十位的同步清零端才允许有效,为下一次同步清零作好准备,故。8421BCD编码的60进制同步级联计数器如图3(a)。

2.片间异步级联法

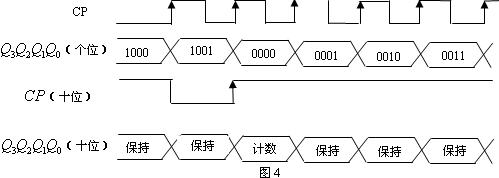

采用片间异步级联时,当个位计数溢出时为十位提供一个有效时钟边沿。由于74LS163是工作在时钟上升沿,为保证个位由9变0时,产生该上升沿,高位时钟,产生十位时钟有效沿的过程如图4。

高位(十位)设计与同步级联相同,完整逻辑图如图3(b)。

【题目4】:如何阅读集成计数器的功能表?

【相关知识】:中规模集成计数器的功能表,计数,清零,置数等。

【解题方法】:中规模集成计数器的主要功能有计数、置数、清零和保持。计数又可分为加法和减法两种,编码方式主要有8421BCD编码的10进制计数器和四位二进制计数器两种。应用集成计数时特别要注意区分清零和置数是异步控制还是同步控制。

【解答过程】:中规模集成计数器的逻辑功能可以用电路框图、逻辑功能表或时序图等描述,应用集成计数器必须学会阅读功能表。

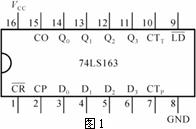

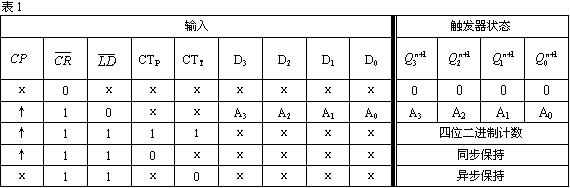

例,图1是集成计数器74LS163的电路框图,其逻辑功能如表1所示,且。

表1中的第一行实现清零功能。清零条件是清零控制端有效,即。由于清零与时钟有效沿无关,故是异步清零,即只要清零输入控制有效(低电平),输出状态立即变成0000。

表1中的第二行实现置数功能。置数条件是:(1)清零控制端无效,置数控制端有效,即;(2)时钟脉冲上升沿触发。由于置数需要时钟有效沿配合,故是同步置数,当置数条件全部满足时

。实现同步置数时,同步控制端必须先有效,等待时钟有效沿到达时实现置数功能,两者时序不能颠倒。

表1中的第三行实现计数功能。从左至右,4位二进制计数功能需要满足的条件是:(1)置数和清零端均无效(由于清零和置数是低电平有效,无效时);(2)同步计数端有效,

;(3)时钟脉冲上升沿触发。

表1中的第四、五行实现同步保持功能。置数和清零端均无效时,同时计数控制端无效时,即或

,即使时钟有效沿到来,触发器状态仍保持不变,实现同步保持功能。

| 上一页12345678下一页 |